# **Accurate DGEMM using Tensor Cores**

Daichi Mukunoki<sup>1</sup>, Katsuhisa Ozaki<sup>2</sup>, Takeshi Ogita<sup>3</sup>

1 RIKEN Center for Computational Science (JAPAN), 2 Shibaura Institute of Technology (JAPAN), 3 Tokyo Woman's Christian University (JAPAN)

#### Introduction

- · As the demand for deep-learning increases, specialized hardware dedicated to low-precision matrix-multiplication, which is the kernel of those tasks, has been developing (e.g., NVIDIA Tensor Core, Google TPU, ARM Matterhorn's Matmul)

- NVIDIA Tensor Cores are a special processing unit that enables 4×4 matrix multiplication operations FP16 inputs with FP32 precision and return the result on FP32. Besides, cuBLAS provides the cublasGemmEx routine using the above Tensor Core operation.

Tensor Core operation with FP32 accuracy

- Markidis et al. [1] proposed a method to achieve nearly the SGEMM equivalent accuracy on the matrices with the dynamic range supported on FP16 using the cublasGemmEx routine.

- In this poster, we present an accurate DGEMM implementation, which has the DGEMM compatible interface and can be computed using cublasGemmEx on Tensor Cores

- Our implementation returns the correctly-rounded result: it supports bitlevel reproducibility and is compatible with other correctly-rounded GEMMs such as ExBLAS [2] and OzBLAS [3]

#### Data and computation precisions on GEMM routines

|                                      | Mat. A | Mat. B | Mat. C | Computation       |

|--------------------------------------|--------|--------|--------|-------------------|

| cublasDgemm                          | FP64   | FP64   | FP64   | FP64              |

| cublasGemmEx<br>(with Tensor Cores†) | FP16   | FP16   | FP32   | FP32              |

| our DGEMM                            | FP64   | FP64   | FP64   | Correctly-rounded |

†Other operations and data formats are also supported through the same interface without Tensor Cores

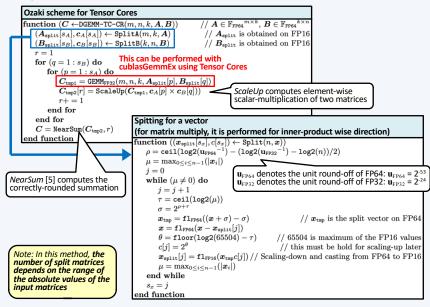

# Method (Ozaki scheme)

- Our method is based on the Ozaki scheme [4], which is an accurate matrix-multiplication algorithm based on the error-free transformation for dot-product/matrixmultiplication.

- In this study, we modified the original version of the Ozaki scheme, which was designed to be computed using DGEMM, to be computed using Tensor Cores on FP64 input/output.

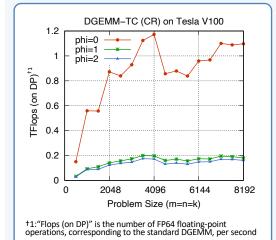

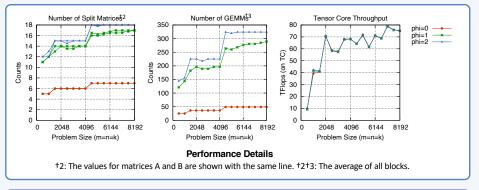

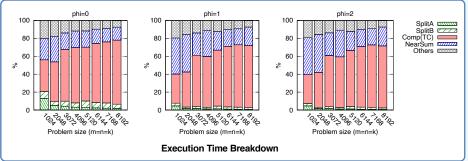

## Performance on Tesla V100

- Environment: NVIDIA Tesla V100 GPU (PCIe-32GB): the theoretical peak performance (with 1.38 GHz) is 7065.6 GFlops on FP64 and 113049.6 GFlops on Tensor Cores, CUDA 10.1, GPU driver version 418.39.

- Performance depends on the input (the number of split matrices depends on the range of the absolute values of the input matrices): matrices are initialized with (rand-0.5)  $\times \exp(\varphi \times \text{randn})$  to vary the floating-point range: 9.3E-10 - 5.0E-01 on  $\varphi$  = 0, 1.5E-09 - 1.6E+02 on  $\varphi = 1$ , and 1.3E-09 – 4.8E+04 on  $\varphi = 2$ .

## Conclusion

- · We presented an accurate GEMM implementation with the DGEMM compatible interface using cublasGemmEx performed on Tensor Cores, which returns the correctly-rounded result on FP64

- The performance depends on the input matrices. For example, for matrices initialized with random numbers having the dynamic range of 1E+9, we achieved approx. 1.2 TFlops

- $\bullet\,$  Although our implementation brings no performance advantage against cuBLAS DGEMM on GPUs that support fast FP64 (1/16 of Tensor Cores), it can be beneficial on hardware with limited FP64 support such as NVIDIA Tesla T4, whose FP64 performance is 1/256 of Tensor Cores.

- Our approach opens the way to utilize Al-oriented hardware, which supports limited FP64 performance, for more general purposes and may impact the system co-design.

- The latest work including some extensions will be published soon.

# Reference and Acknowledgement

[1] Markidis, S., Chien, S.W.D., Laure, E., Peng, I.B., Vetter, J.S.: NVIDIA Tensor Core Programmability, Performance Precision. In: 2018 IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW). pp. 522–531 (2018) [2] S. Collange, D. Defour, S. Graillat, R. lakymchuk: Numerical reproducibility for the parallel reduction on multi-and many-core architectures, Parallel Computing, Vol. 49, pp. 83-97, 2015. [3] Mukunoki, D., Ogita, T., Ozaki, K.: Reproducible BLAS Routines with Tunable Accuracy Using Ozaki Scheme for Many-core Architectures. In: 13th International Conference on Parallel Processing and Applied Mathematics (PPAM2019) (2019), (to appear) [4] K. Ozaki, T. Ogita, S. Oishi, S. M. Rump, "Error-free transformations of matrix multiplication by using fast routines of matrix multiplication and its applications," Numerical Algorithms, Vol. 59, No. 1, pp. 95-118, 2012. [5] S. Rump, T. Ogita, S. Oishi, "Accurate floating-point summation part II: Sign, k-fold faithful and rounding to nearest," SIAM Journal on Scientific Computing, Vol. 31, No. 2, pp. 1269–1302, 2008.

\* This research was partially supported by MEXT as "Exploratory Issue on Post- K computer" (Development of verified numerical computations and super high- performance computing environment for extreme researches) and the Japan Society for the Promotion of Science (JSPS) KAKENHI Grant Number 19K20286. This research used computational resources of Cygnus provided by Multidisciplinary Cooperative Research Program in Center for Computational Sciences, University of Tsukuba.